2020-06-12

项目成员:唐敏哲、李正浩、樊泰扬、陆煜晨

指导老师:潘权 教授

光通信芯片是国家和企业在光通信行业的核心竞争力,随着目前5G时代的到来,竞争势必愈发激烈。在高端芯片产业,国外芯片厂商一直以来保持垄断地位,严重制约了我国高端产业的发展,威胁着国家战略安全。光接收机作为光通信芯片的核心组成部分,对我国光通信系统性能提升、社会发展及国家占领高速集成芯片市场具有重要意义。其中SerDes 模拟前端芯片更是实现高速光接收机的重要技术。

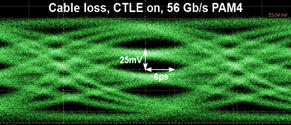

在本项目中,我们旨在对CMOS工艺集成的高速SerDes模拟前端芯片进行研究。在TSMC 40nm CMOS工艺下,设计出一款使用基于四电平脉冲幅度调制(4-Level Pulse Amplitude Modulation,Pam4)传输方式的56Gb/s高速SerDes模拟前端芯片。采用创新性的电路模块,并将前端电路集成于单一芯片,减少芯片面积,降低总功耗,并进一步提高速率与带宽。 本项目完成了对AFE芯片的设计、流片以及测试,测试结果符合预期性能指标。接下来的工作将对所设计的芯片进行进一步的优化,以提高其性能并尝试降低功耗。